# RESEARCH ARTICLE

OPEN ACCESS

# Implementation of Universal Asynchronous Receiver and Transmitter

Bennuri Ashwini, Payata Srikanth Yadav, T. Ashok Kumar Reddy: Students of ECE, M. Rajesh, Assitant Professor, B.Krishna, Associate Professor Kite College of Professional Engineering Sciences-Shabad

# ABSTRACT

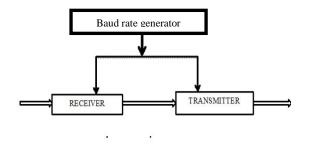

Universal Asynchronous Receiver Transmitter (UART) is the serial communication protocol that is used for data exchange between computer & peripherals. UART is a low velocity, short-distance, low-cost protocol. UART includes three modules which are received, the baud rate generator and transmitter. The UART design with Very High Description Language can be integrated into the Field Programmable Gate Array to achieve stable data transmission and to make system reliable and compact. In the result and simulation part, this project will focus on check the receive data with error free & baud rate generation at different frequencies. Before synthesizing of UART a baud rate generator is incorporated into the system. We use the frequency divider which sets itself to required frequency for the functionality at lower frequency. All modules are designed using VERILOG and implemented on Xilinx Suite development board.

# I. INTRODUCTION

UART transmitter fetches a data word in parallel format and directing the UART to transmit it in a serial format. Likewise, the Receiver must detect transmission, which receive the data in serial format, and stores the data in a parallel format. As the UART is asynchronous in working, the receiver cannot acknowledge the incoming of data; receiver generates a local clock for the synchronisation of transmitter when start bit gets received. There is no need of generating separate clock by the transmitter. Transmitter and receiver agree timing parameters in advance for synchronizing the sending and receiving units.

UART is an integrated circuit which plays a predominant role in serial communication. ART acquires the function of conversion between the serial and parallel data. It provides Data Transfer between two systems is at great distance and there is reduction of signal distortion.

Parallel communication is a short distance communication with lot of multi bit address bus and data bus.

Serial communication is a long distance transmission communication and is widely used. But sometimes could not meet requirements due to Baud rate equipments. For low speed peripheral devices we use Serial communication. For complete communication FIFO Principle is used.

# Why do we implement UART?

As UART can be used when there is no requirement for high speed and is inexpensive.

The protocol can be highly configurable. The major part is matching the serial bus baud rate.

#### Present Work

This project specifies and checks the receiver data with error free & baud rate generation at different frequencies.

## **Implementation of UART**

The internal module of transmitter consists of parallel to serial converter and at the receiver end consists of serial to parallel converter.

In Asynchronous serial communication, sharing the clock with one another is not required, but the sender and receiver must agree timing parameters. Asynchronous transmission provides high reliability and long transmission distance. Hence, UART is used in data exchange between computer and peripherals.

UART allows full duplex communication in serial link. This paper uses Verilog HDL to implement the core functions of Serial communication.

UART communication needs only two signal lines (Rxd, Txd) for full duplex data communication.Txd is the transmit side which acts as output and Rxd is the receiver which acts as input. There are two states in the signal line, using logic 1(high) and logic 0 (low) to distinguish respectively.

#### Advantages

- 1. High bandwidth solution.

- 2. Line break and false start bit detection.

- 3. Reconfigurable.

# II. BLOCK DIAGRAM BAUD RATE GENERATOR

Baud Rate Generator is actually a frequency divider. The frequency clock produced by the baud

rate generator is not exactly the baud rate clock, but 16 times the baud rate clock. For sampling there exists the ideal time at the middle point of serial data bit. This output clock generated can be used as the receive reference clock by the receiver UART.

#### **RECEIVER MODULE**

During the UART reception, the serial data and the receiving clock are asynchronous, so it is very important to correctly determine the start bit of a frame data.

RXD transfers into logic 0 from logic 1 which resembles as the beginning of a data frame. Once the start bit gets identified, next bit begin to count the rising edge of the baud clock, and when counting considers the sample RXD. Each value of the logic level gets placed in the register rbuf [7, 0] in order.

When the count equals 8, we can ensure that all the data bits are received, and are converted into a byte parallel data.

UARTs resynchronize the internal clocks on change of the data line. Due to resynchronisation they reliably receive when the transmitter is sending at a slightly different speed than it should. The other UARTs do not support this, and they resynchronize on the falling edge of the start bit only, and then read the center of each expected data bit, and this works if the broadcast data rate is accurate for allowance of the stop bits for reliability. Three error detection signals are commonly used in UART:

- Parity Error used to justify the whether there 1. exists even or parity by focussing on 1's.

- 2. Overrun Error specifies whether data is overwritten than expected.

- 3. A framing error occurs when the designated start and stop bits are not valid.

#### **TRANSMITTER MODULE**

The operation of transmit module is conversion of the sending 8-bit parallel data into serial data, adds start bit at the MSB of the data as well as the parity and stop bits at the LSB of the data. When the UART transmit module is reset, the transmit module immediately gets activated to send the data. The output appears as 1 start bit, 8 data bits, 1 parity bit and 1 stop bit. The parity bit is specified as the output. Finally, stop bit displays logic 1.

Depending on the manufacturer, specifies the different representations for UARTs Intel called their 8251 device as a "Programmable Communication Interface". The technique cannot send or receive data at high speed, but provides level of compatibility.

#### **Importance of UART**

1. Synchronisation Controls the reception and transmission time of the data

2. Increases the accuracy and reduces the effect of the noise

# **UART Functioning**

For the Full-duplex data communication UART needs only two signal lines (Rxd, Txd) to complete. Txd is the transmit side, which acts the output of UART; Rxd is the receiver, which is used as the input of UART. The two states in the signal line can be distinguished using logic 1 (high) and logic 0 (low).

The start bit is used for alerting the receiver that a word of data is about to be sent, and to force the clock in the receiver to get synchronized with the clock in the transmitter.

When the transmitter is idle state, the data line is in the logic high state. After the first bit, the individual bits are sent, with the least significant bit being sent first. Each bit in the transmission has to maintain exactly same amount of time and the receiver concentrates at approximately halfway for determining if bit is 0 or 1. The sender does not make sure when the receiver expected at the value of bit.

When the receiver receives all the bits of data word it concentrates on parity bit and then generates the stop bit. If the stop bit does not appear then it results in framing error. This is due to the variations in clocks of receiver and transmitter module.

Irrespective of the received data the UART itself eliminates the start, parity and stop bits. If there is a new word ready for transmission the system gets selfsynchronised. If there is no data to transmit, the transmission line can be idle.

SIMULATED OUTPUT OF TRANSMITTER

SIMULATED OUTPUT OF RECEIVER

| a tim (P.20x0 - (Detautwork)*)      |                                                        |                                               |                     |                                          | 1    |

|-------------------------------------|--------------------------------------------------------|-----------------------------------------------|---------------------|------------------------------------------|------|

| File Edit View Simulation 1         | Window Layout Help                                     |                                               |                     |                                          |      |

|                                     | 0 0 0 0 M A I I C                                      | SH +                                          | / / / / / (d) the s | 27 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |      |

| Instances and Processes ** C 6      | H H Obsects                                            | ** C # H                                      |                     | ACCRETATION OF                           |      |

|                                     | Simulation Objects for u_povr                          |                                               |                     |                                          |      |

| Instance and Freezes Name           |                                                        | Name Name                                     | Value 2 m           | 100 mi                                   |      |

|                                     | D I Name Value                                         |                                               | 1 M                 |                                          |      |

| 5- W. ACM                           | at a res readate a                                     | 12 14                                         | ° U                 |                                          |      |

|                                     | perit state(2.0) wave                                  | Image: A 10 A 1 | • 050 -             | 000                                      |      |

|                                     | state(r.ct                                             | CO 100 CO                                     | 010                 | e 0                                      |      |

|                                     | FIRE dated in                                          | 120 100 100                                   | • 033               | 0 J J                                    |      |

|                                     | Frec dation of a                                       |                                               | 100                 | 20                                       |      |

|                                     | and reserves a                                         |                                               | + 101               | 191                                      |      |

|                                     | par.data/47.00 HIGHNERKE                               | 2 P 🐏 wor                                     | 1000                | 2000                                     |      |

|                                     | a shaffers as                                          | 1.1                                           |                     |                                          |      |

|                                     | FEEd_bitoMPL. HORE                                     |                                               |                     |                                          |      |

|                                     | - retraustit w                                         | . 11                                          |                     |                                          |      |

|                                     | s recountry a                                          | 1 120                                         |                     |                                          |      |

|                                     | a 101 A                                                | 0.40                                          |                     |                                          |      |

|                                     | , to 0                                                 | 125                                           |                     |                                          |      |

|                                     | r_start[2:0] 0:00                                      |                                               |                     |                                          |      |

|                                     | r watten ass                                           |                                               |                     |                                          |      |

|                                     | r.tamptel2tH 300                                       |                                               |                     |                                          |      |

|                                     |                                                        |                                               | X 11 30 1.471 mil   |                                          |      |

| •                                   | a word_ten(30) 1000                                    |                                               | 4 3 4               |                                          | -    |

| A Instanc Ch Memory   Discussion    |                                                        |                                               | Default.vcfg*       |                                          |      |

| Console                             |                                                        |                                               |                     |                                          | 9 H  |

| Date PL28vd (signature 0x1048(149)) |                                                        |                                               |                     |                                          | -    |

| This is a Pull version of Hen.      |                                                        |                                               |                     |                                          | 111  |

|                                     |                                                        |                                               |                     |                                          |      |

|                                     |                                                        |                                               |                     |                                          |      |

| Plano-                              |                                                        |                                               |                     |                                          |      |

| Entropy In                          |                                                        |                                               |                     |                                          |      |

| Console Compliation Log             | <ul> <li>Dreakpoints 66 Find in Files files</li> </ul> | suits in tearch fireads                       |                     |                                          | -    |

|                                     |                                                        |                                               |                     | Sim Time 1,000,00                        | 0.04 |

| (2) (2) (2)                         | > 🗲 📷 🗾                                                |                                               |                     | <ul> <li> <ul> <li></li></ul></li></ul>  |      |

|                                     |                                                        |                                               |                     |                                          |      |

SIMULATED OUTPUT OF UART

# **III. CONCLUSION**

In this paper, we proposed a design of UART with inbuilt Baud Rate generator. The design is successfully simulated using Xilinx ISE 14.2 suite software. The results are stable and reliable and show the correct functionality. Hence, we can improve the speed of UART by sending 16 bits per second of time. But by sending 16 bit ,it become more complex to count number of clock bit per unit time, so this can be overcome by using multichannel UART in future.

## **IV. FUTURE SCOPE**

This can be implemented through hardware if an FPGA kit is available instead of software implementation. UART Channels can be increased to speed up the data transmission.

# REFERENCES

- HU Hua, BAI Feng-e. Design and Simulation of UART Serial Communication Module Based on Verilog -HDL [J]. J ISUANJ I YU XIANDA IHUA 2008 Vol. 8 Frank Durda Serial and UART Tutorial. Uhclem@freebsd.org

- [2] Amanpreet Kaur, Amandeep Kaur, "An approach for designing a universal asynchronous receiver transmitter (UART)", International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, Issue 3, May- Jun 2012, pp.2305-2311

- [3] Liakot Ali , Roslina Sidek, Ishak Aris, Alauddin Mohd. Ali, Bambang Sunaryo Suparjo. Design of a micro - UART (2004) 257–268.

# ABOUT AUTHORS

BENNURI ASHWINI as a student of IV year Electronics and Communication engineering Department at KITE College of Professional engineering sciences, SHABAD, Ranga Reddy Dist.

PAYATA SRIKANTH as a student of IV year Electronics and Communication engineering Department at KITE College of Professional engineering sciences, SHABAD, Ranga Reddy Dist.

T.ASHOK KUMAR REDDY as a student of IV year Electronics and Communication engineering Department at KITE College of Professional engineering sciences, SHABAD, Ranga Reddy Dist.

B.KRISHNA completed B.Tech in Electronics Communication Engineering and Paul-Raj Engineering from Dr. College Bhadrachalam (JNTUH) and M.Tech (VLSI-SD) From SITAMS- Chittoor (JNTUH) . His interested Research area is Analog and mixed signal systems design. He has total of 9 years of teaching experience. Right now He is working as Assoc. Professor in the department of Electronics and Communication Engineering in KITE College of professional Engineering Scienes, Shabad ,HYDERABAD .